|

|

BCH10 Core, Parameterizable Compact BCH Codec

|

|

General

Description |

|

|

Targets the high-performance very-low-latency error correction ASIC applications with high k (about 500) and small t (3-5) using BoseChaudhuriHocquenghem codes (BCH codes) that prioritize latency over size. |

|

The latency of the encoder core is 2 clocks. The decoder latency is 5-7 clocks input-to-output data.

|

|

|

Symbol |

|

|

|

|

|

Key

Features |

|

|

High performance, low latency |

|

Small size (75K gates for k=298, t=4) configuration, the core uses just 17K gates in ASIC) |

|

Entirely self-contained (no external RAM required) |

|

Data inputs and outputs have flip-flops attached to the pins |

|

|

|

| |

| |

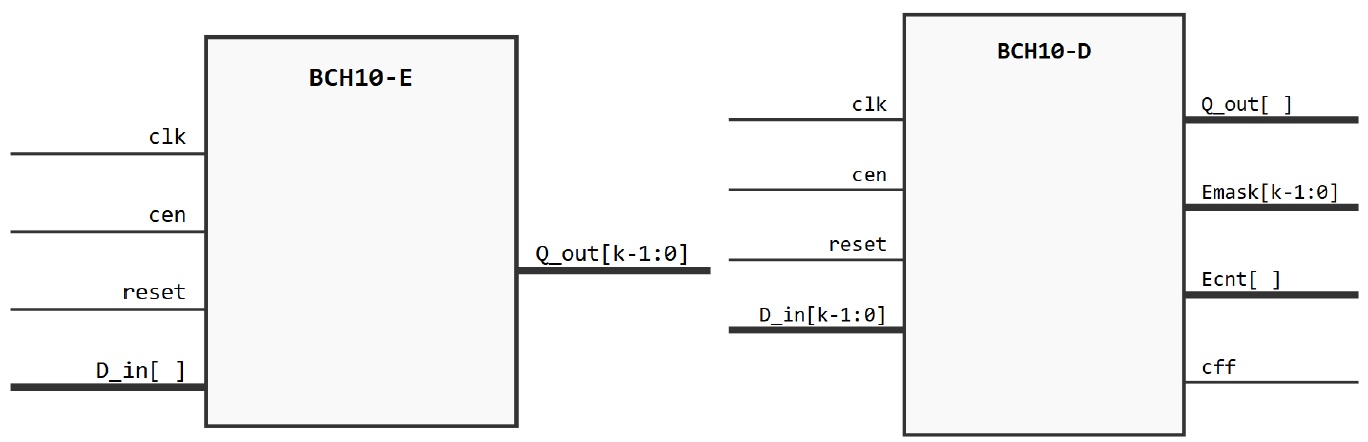

Encoder Core Interface Signals (BCH10-E)

| Name |

Direction |

Width |

Description |

| clk |

Input |

1 |

Clock signal |

| cen |

Input |

1 |

Clock enable signal. When driven low, it pauses the operation of the core |

| reset |

Input |

1 |

Active HIGH asynchronous reset signal. Drives internal registers to their

default state independent of the clock. |

| D_in |

Input |

|

Data to be encoded |

| Q_out |

Output |

k |

Codeword |

|

Decoder Core Interface Signals (BCH10-D)

| Name |

Direction |

Width |

Description |

| clk |

Input |

1 |

Clock signal |

| cen |

Input |

1 |

Clock enable signal. When driven low, it pauses the core and pipeline

state. |

| reset |

Input |

1 |

Active HIGH asynchronous reset signal. |

| D_in |

Input |

k |

Received codeword |

| Q_out |

Output |

|

Corrected data payload. Parity bits are stripped. |

| Emask |

Output |

k |

Errors mask indicating the exact locations of detected errors |

| Ecnt |

Output |

|

Number of errors detected, in the range 0-t. If the number of errors in

the input word is greater than t, the core is unable to correct the errors

and Q_out and Emask shall not be relied upon |

| cff |

Output |

1 |

Correction Failed Flag: Asserts if there are too many errors. All other

outputs in this case are most likely invalid. |

|

|

| |

|

| |

| |

|

Deliverables |

|

HDL Source Licenses

|

|

Synthesizable Verilog

RTL source code |

|

Test bench

(self-checking) |

|

Test vectors |

|

Expected results |

|

Software Development Kit (SDK)

|

|

User Documentation

|

|

|

|

| |

|

| |

|